XC6VLX240T-1FFG1156小知识 一般说明 XC6VLX240T-1FFG1156是目标设计平台的可编程芯片基础,可提供集成的软件和硬件组件,使设计人员能够在开发周期开始时立即专注于创新。使用第三代ASMBLTIM(高级硅模块)列架构...

” XC6VLX240T “ 的搜索结果

基于VPX架构,主体芯片为两片 TI DSP TMS320C6678,两片Virtex-6 XC6VLX240T-ff1156 FPGA,1个RapidIO Switch。FPGA连接FMC子卡。FPGA片外挂接2簇32bit DDRIII SDRAM,大容量支持2GB。每片FPGA还通过EMIF总线连接一片...

XC5VLX115T-110T XILINX FPGA开发板 PROTEL设计原理图+PCB布局封装文件,RPOTEL版原理图及PCB器件封装,pcb网表已经导出,与原理图一致,并未布局布线(项目中PCB为14层板,PCB版图不于提供) 系统主要硬件包括 1、...

基于Xilinx Virtex-6 XC6VLX240T 和TI DSP TMS320C6678的信号处理板 1、板卡概述 板卡由我公司自主研发,基于VPX架构,主体芯片为两片 TI DSP TMS320C6678,两片...

基于6U VPX的 XC7VX690T+C6678的双FMC接口雷达通信处理板 一、板卡概述 高性能VPX信号处理板基于标准6U VPX架构,提供两个...

基于TMS320C6678、FPGA XC5VLX110T的6U CPCI 8路光纤信号处理卡 北京太速科技有限公司 基于CPCI架构,符合CPCI2.0标准,采用两片TI DSP TMS320C6678...

XILINX FPGA(XC5VLX155T)_SRAM_USB发板protel硬件原理图+PCB,采用14层板设计,板子大小为260x200mm,双面布局布线,FPGA芯片选用Xilinx高端系列V5中的1片 XC5VLX155T和2片XC5VLX110T,3款USBPHY 接口芯片选用CY7C...

基于TMS320C6678、FPGA XC5VLX110T的6U CPCI 8路光纤信号处理卡1、板卡概述 本板卡由我公司自主研发,基于CPCI架构,符合CPCI2.0标准,采用两片TI DSP TMS320C6678芯片和Xilinx公司V5系列FPGA XC5VSX95T-1FF1136...

基于5VLX110T FPGA FMC接口...由一片Xilinx公司的XC5VLX110T-1FF1136/XC5VSX95T-1FF1136/XC5VFX70T-1FF1136芯片组成。FPGA接1片DDR2内存条 2GB,32MB Nor flash存储器,用于存储程序。外扩 SATA、PCI、PCI express...

XC5VLX30T-2FF323I Virtex-5 LXT FPGA IC产品参数。

FPGA的配置工作主要有两部分,连接CPU与AX88180,和连接CPU与S1R72V17。 连接CPU与AX88180CPU与AX88180的连接可以参考AX88180 datasheet上的附录A,采用32bit数据线连接方式: 主要是32位数据线与CPU DATA线相连,...

柔性直流输电系统中用于控制与测量的FS系统,适用于风电和太阳能发电的并网快速数值计算和闭环控制,以及与直流输电系统的换流器有关的特殊控制功能,包括门控单元的信号处理。对于TDM板卡,每个板子的主FPGA有9对...

基于 Xilinx FPGA XC5VL +CY7C68000单片机项目应用开发板硬件(原理图+PCB)DDB工程文件,Protel 99se 设计的项目工程文件,包括原理图及PCB印制板图,可用Protel或 Altium Designer(AD)软件打开或修改,都已经制板...

目录 1、时钟网络与全局缓冲 2、全局时钟资源的使用方法 2.1、IBUFG+BUFG 2.2、IBUFG+DCM(PLL)+BUFG 3、全局时钟系统使用的问题与注意事项 ...4、全局时钟系统使用举例 ...在 FPGA基础知识 1(FPGA 内部结构)文章中...

Xilinx7SeriesFPGA型号列表SupportedDevice(1),(2)CoreVersionSignalingEnvironmentVirtex-5XC5VFX70T-FF1136-2C/I(3)(regionalclock)v43.3VonlyVirtex-5XC5VLX50-FF1153-2C/I(3)(regionalclock)v43.3Von...

... 摘要:在高性能雷达信号处理机研制中,高速...业界广泛使用的Xilinx公司Virtex-6系列FPGA支持多种高速串行通信协议,本文针对其中较为常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三种协议进行了测试

时钟资源为了更好的控制时钟,Virtex-6器件分成若干个时钟区域,最小器件有6个区域,最大器件有18个区域。每个时钟区域高40个CLB。在时钟设计中,推荐使用片上专用的时钟资源,不推荐使用本地时钟(如逻辑产生的时钟...

VPX613是一款基于6U OpenVPX总线架构的超高速信号采集、处理、回放板卡,该板卡包括1片单通道5.2Gsps DAC(可选兼容4Gsps版本),1片单通道5Gsps ADC(可配置成2通道2.5G或4通道1.25G),1片用于信号处理的高端...

在高性能雷达信号处理机研制中...业界广泛使用的Xilinx公司Virtex-6系列FPGA支持多种高速串行通信协议,本文针对其中较为常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三种协议进行了测试及对比分析。...

VPX613是北京青翼科技研发的一款基于6UOpenVPX总线架构的超高速信号采集、处理、回放板卡,该板卡包括1片单通道5.2Gsps DAC(可选兼容4Gsps版本),1片单通道5Gsps ADC(可配置成2通道2.5G或4通道1.25G),1片用于...

业界广泛使用的Xilinx公司Virtex-6系列FPGA支持多种高速串行通信协议,本文针对其中较为常用的Aurora 8B/10B和PCI Express 2.0,Serial RapidIO 2.0三种协议进行了测试及对比分析。首先搭建了基于Virtex-6 FPGA的...

个人原创,转载请注明出处 环境说明: python32位,版本3.7.3 理论上3.4以上版本可行 直接上代码,通俗易懂 #!/usr/bin/env python3 # _*_ coding: utf-8 _*_ # File : 一键打包exe.py ...# Date ...

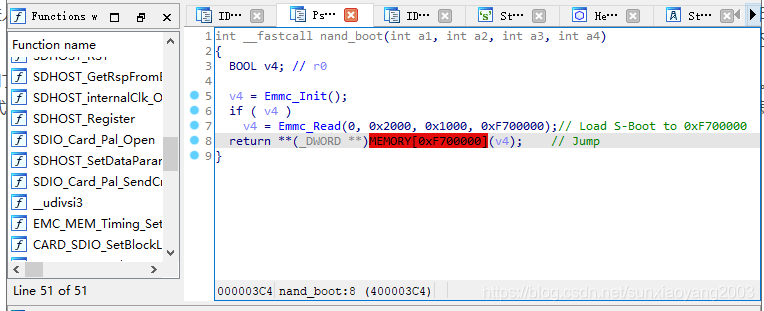

u-boot部分: normal_mode -> vlx_nand_boot -> vlx_entry 8f860134 : 8f860134: e92d4008 push {r3, lr} 8f860138: eb000869 bl 8f8622e4 8f86013c: e30017de

这篇文章主要针对Xilinx家V6和K7两个系列的PFGA,在Linux和Windows两种系统平台下,基于Xilinx的参考案例XAPP1052的基础上,设计实现了总线主控DMA(Bus Master DMA),透明映像内存空间和中断机制,在实际工程实践...

第一种代码的界面如下:(有缺点,中文乱码)

报文的起始位是显性位,起始位来临时触发硬同步,启动位周期定时,按照 波特率设计数值计算计数器数值,该过程发生在SYNC段,发生时间点记为T1, 假设总线第二位数据位为隐性电位,由于出现信号边沿,触发重同步过程...

为了更好的控制时钟,Virtex-6器件分成若干个时钟区域,最小器件有6个区域,最大器件有18个区域。每个时钟区域高40个CLB。在时钟设计中,推荐使用片上专用的时钟资源,不推荐使用本地时钟(如逻辑产生的时钟)。 ...

推荐文章

- GPT-ArcGIS数据处理、空间分析、可视化及多案例综合应用

- 在Debian 10上安装MySQL_debian mysql安装-程序员宅基地

- edge 此项内容已下载并添加到 Chrome 中。_一个小扩展,解决Chrome长期以来的大痛点...-程序员宅基地

- vue js 点击按钮为当前获得焦点的输入框输入值_vue获得当前获得焦点的元素-程序员宅基地

- Android 资源文件中@、@android:type、@*、?、@+含义和区别_@android @*android-程序员宅基地

- python中的正则表达式是干嘛的_Python中正则表达式介绍-程序员宅基地

- GeoGeo多线程_geo 多线程-程序员宅基地

- phpstudy的Apache无法启动_phpstudy apache无-程序员宅基地

- 数据泵导出出现ORA-31617错误-程序员宅基地

- java基础巩固-宇宙第一AiYWM:为了维持生计,两年多实验室项目经验之分层总结和其他后端开发好的习惯~整起_java两年经验项目-程序员宅基地